Compiling various open-source projects to extract their best features, we aim to create a streamlined full-stack platform for SoC (System on a Chip) design verification.

- Chipyard:

An Agile RISC-V SoC Design Framework with in-order cores, out-of-order cores, accelerators, and more.

-

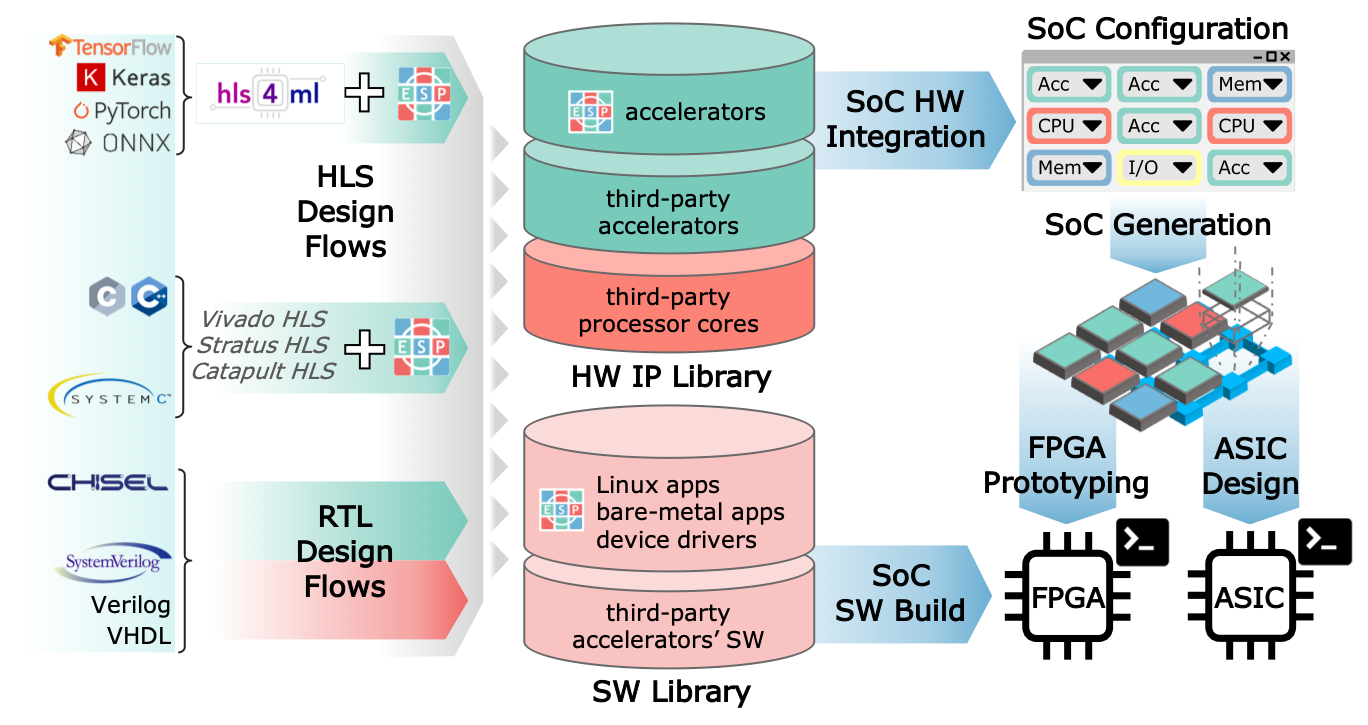

ESP Embedded Scalable Platforms: Heterogeneous SoC architecture and IP integration made easy.

-

OpenTitan: OpenTitan: Open source silicon root of trust.

-

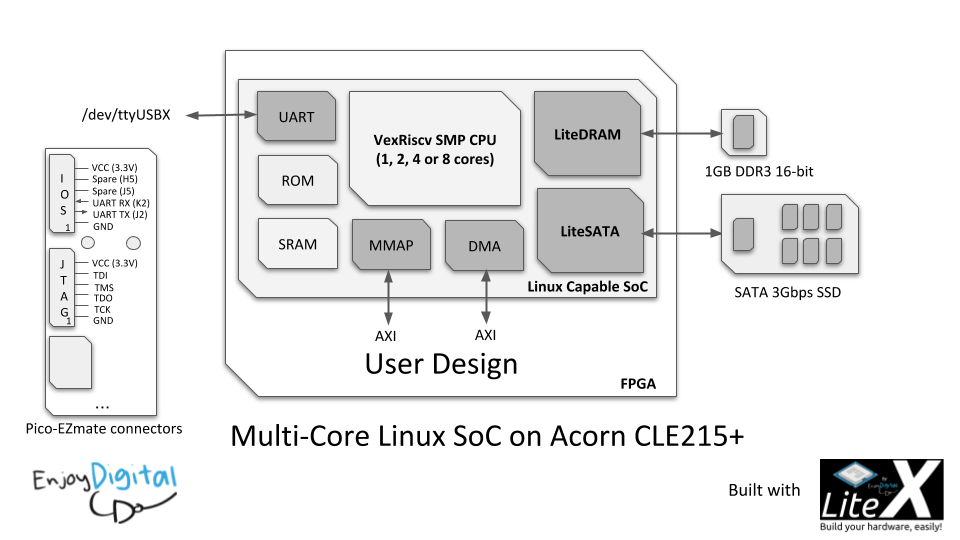

litex: LiteX is developed and used by Enjoy-Digital since 2012 to co-develop full-systems with our partners and provide an convenient and efficient solutions to create SoCs on FPGA based systems. Here are some of the last project we worked on with our partners.

-

migen:A Python toolbox for building complex digital hardware.

from migen import * from migen.build.platforms import m1 plat = m1.Platform() led = plat.request("user_led") m = Module() counter = Signal(26) m.comb += led.eq(counter[25]) m.sync += counter.eq(counter + 1) plat.build(m)

-

cocotb: cocotb, a coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python.

- riscv-mini:

Simple RISC-V 3-stage Pipeline in Chisel.

- riscv-sodor:

Educational microarchitectures for risc-v isa.

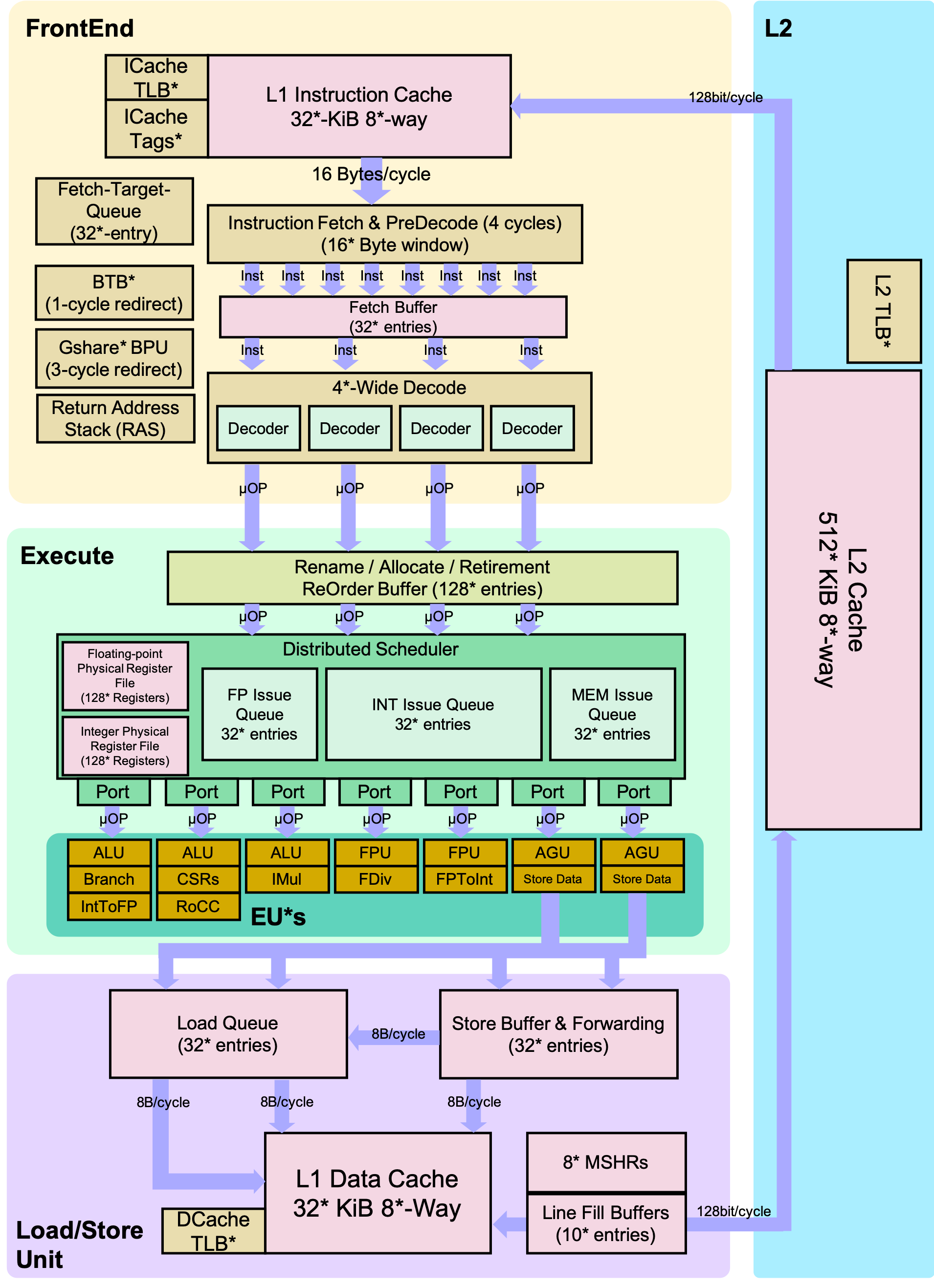

- riscv-boom:

SonicBOOM: The Berkeley Out-of-Order Machine

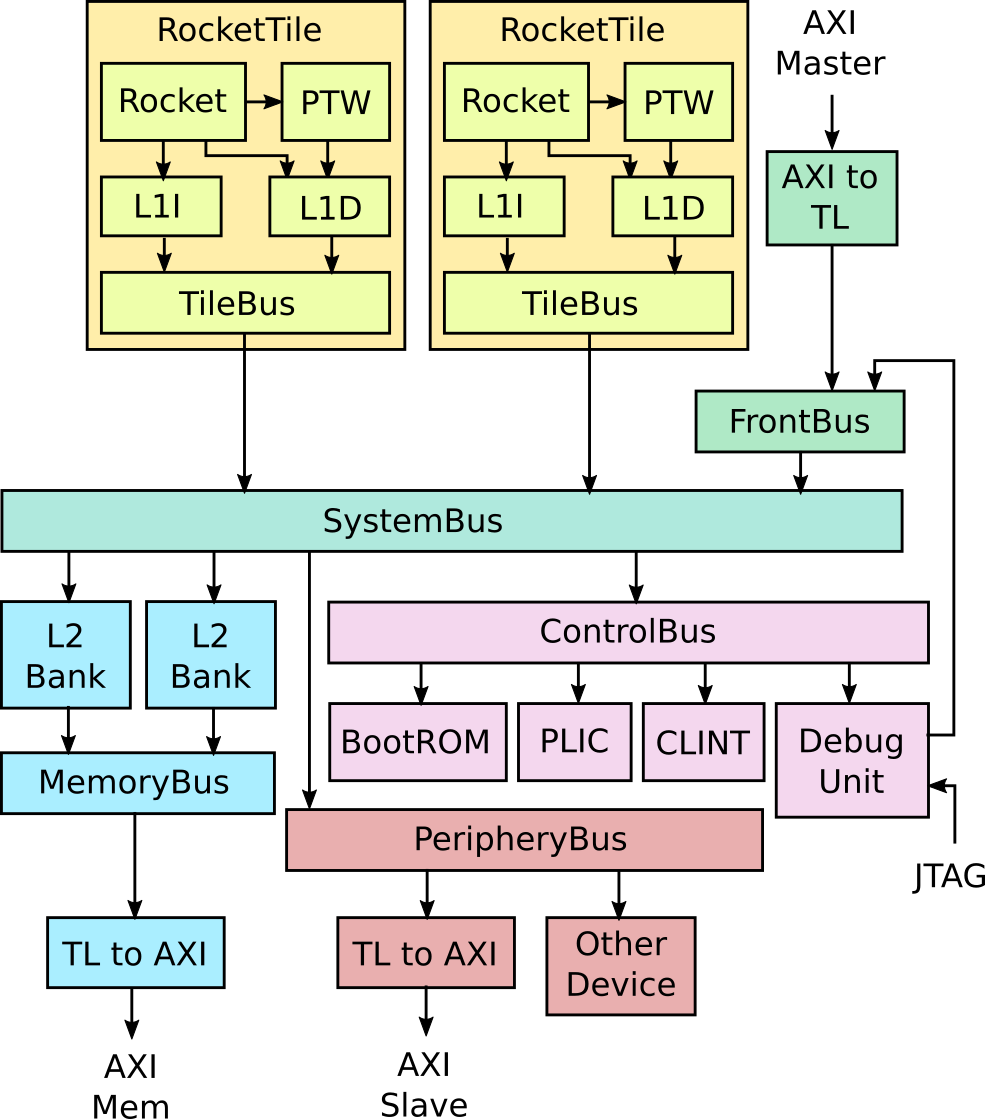

- rocket-chip:

Rocket Chip Generator

- Ibex:

Ibex is a production-quality open source 32-bit RISC-V CPU core written in SystemVerilog. The CPU core is heavily parametrizable and well suited for embedded control applications. Ibex is being extensively verified and has seen multiple tape-outs. Ibex supports the Integer (I) or Embedded (E), Integer Multiplication and Division (M), Compressed (C), and B (Bit Manipulation) extensions.

- testchipip: https://github.com/x-tinkerer/testchipip

- riscv-isa-sim: https://github.com/riscv-software-src/riscv-isa-sim

- Ripes:

A graphical processor simulator and assembly editor for the RISC-V ISA.

- Performance Modeling: https://github.com/x-tinkerer/riscv-perf-model

-

Xiangshan: Open-source high-performance RISC-V processor

- XiangShan Frontend Develop Environment: https://github.com/x-tinkerer/xs-env

-

gem5: The gem5 simulator is a modular platform for computer-system architecture research, encompassing system-level architecture as well as processor microarchitecture.

- arm-gem5-rsk :https://github.com/x-tinkerer/arm-gem5-rsk Official repository of the Arm Research Starter Kit on System Modeling using gem5

-

The Simulation Engine - SimEng SimEng is a framework for building modern, cycle-accurate processor simulators. Its goals are to be:

- Fast, typically 4-5X faster than gem5

- Easy to use and modify to model desired microarchitecture configurations. New cores can be configured in just a few hours

- Scalable, from simple scalar microarchitectures up to the most sophisticated, superscalar, out-of-order designs

- Capable of supporting a wide range of instruction set architectures (ISAs), starting with AArch64 and RISC-V, but eventually including x86, POWER, etc.

- Accurate, aiming for simulated cycle times being within 5-10% of real hardware

- Open source, with a permissive license to enable collaboration across academia and industry

- Modelling_Apple_M1_CPU_Architecture :https://github.com/x-tinkerer/Modelling_Apple_M1_CPU_Architecture

- DRAMSys

DRAMSys a SystemC TLM-2.0 based DRAM simulator.

-

DRAMsim3 DRAMsim3: a Cycle-accurate, Thermal-Capable DRAM Simulator.

-

Gem5 integration: works with a forked Gem5 version, see https://github.com/umd-memsys/gem5 at dramsim3 branch for reference.

-

SST integration: see http://git.ece.umd.edu/shangli/sst-elements/tree/dramsim3 for reference. We will try to merge to official SST repo.

-

ZSim integration: see http://git.ece.umd.edu/shangli/zsim/tree/master for reference.

-

-

QEMU: is a generic and open source machine emulator and virtualizer.

-

unicorn: Unicorn CPU emulator framework (ARM, AArch64, M68K, Mips, Sparc, PowerPC, RiscV, S390x, TriCore, X86)

- vivado-risc-v: Xilinx Vivado block designs for FPGA RISC-V SoC running Debian Linux distro。

-

riscv-gnu-toolchain GNU toolchain for RISC-V, including GCC.

--with-binutils-src --with-gcc-src --with-gdb-src --with-glibc-src --with-linux-headers-src --with-llvm-src --with-musl-src --with-newlib-src --with-pk-src --with-qemu-src --with-spike-src- riscv-tools-feedstock: https://github.com/ucb-bar/riscv-tools-feedstock

- esp-tools-feedstock: https://github.com/ucb-bar/esp-tools-feedstock

OSS CAD Suite: Multi-platform nightly builds of open source digital design and verification tools

- Yosys RTL synthesis with extensive Verilog 2005 support

- Amaranth refreshed Python toolbox for building complex digital hardware

- Migen Python toolbox for building complex digital hardware

- ABC A System for Sequential Synthesis and Verification

- GHDL VHDL 2008/93/87 simulator (linux-x64 and darwin-x64 platforms only)

- GHDL plugin VHDL synthesis based on GHDL (linux-x64 and darwin-x64 platforms only)

- sby a front-end driver program for Yosys-based formal hardware verification flows.

- mcy Mutation Cover with Yosys

- eqy Equivalence Checking with Yosys

- sby-gui GUI for sby

- aiger AIGER tools including bounded model checker

- avy Interpolating Property Directed Reachability tool

- Boolector SMT solver and BTOR model checker

- Yices 2 SMT solver

- Super prove ABC-based AIGER hardware model checker (linux-x64 platform only)

- Pono an SMT-based model checker built on smt-switch

- Z3 SMT solver

- Bitwuzla SMT solver

- nextpnr a portable FPGA place and route tool (generic, ice40, ecp5, machxo2, nexus, gowin)

- Project IceStorm tools for working with Lattice ICE40 bitstreams

- Project Trellis tools for working with Lattice ECP5 bitstreams

- Project Oxide tools for working with Lattice Nexus bitstreams

- Project Apicula tools for working with Gowin bitstreams

- openFPGALoader universal utility for programming FPGA

- dfu-util Device Firmware Upgrade Utilities

- ecpprog basic driver for FTDI based JTAG probes, to program ECP5 FPGAs

- ecpdap program ECP5 FPGAs and attached SPI flash using CMSIS-DAP probes in JTAG mode

- fujprog ULX2S / ULX3S JTAG programmer

- openocd Open On-Chip Debugger

- icesprog iCESugar FPGA board programmer

- iceprogduino Olinuxino based programmer for iCE40HX1K-EVB

- TinyFPGA USB Bootloader

- TinyFPGA-B TinyFPGA B2 Board programmer

- iceFUN iceFUN Programmer

- GTK Wave fully featured GTK+ based wave viewer

- verilator Verilog/SystemVerilog simulator

- iverilog Verilog compilation system

- cocotb coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python

F4PGA:FOSS Flow For FPGA

| Project Name | Description | Repositories |

|---|---|---|

| Caliptra | The Caliptra project focuses on development of HW and SW IP for the Caliptra Root of Trust | - caliptra - caliptra-rtl - caliptra-sw - caliptra-ureg - caliptra-dpe |

| OpenFASOC | Fully Open Source Automated Analog Block Generation built on top of OpenROAD, Magic, Netgen, Klayout and Ngspice | - OpenFASOC - idea-fasoc |

| RocketChip | The SoC generator instantiates the RISC-V Rocket Core and relevant component. | - rocket-chip |

| SV tests | SystemVerilog test framework for checking SV spec support coverage in various open source tools | - sv-tests |

| Verible | Parse SystemVerilog (IEEE 1800-2017) with a suite of SystemVerilog developer tools | - verible |

| FPGA Interchange format | Vendor agnostic FPGA devices and designs description for interoperability between different FPGA tools | - fpga-interchange-schema |

| Surelog and UHDM | SureLog: SystemVerilog 2017 Pre-processor, Parser, UHDM Compiler. UHDM: Hardware Data Model framework. | - Surelog - UHDM - UHDM-integration-tests |

| F4PGA | Free and open source toolchain for FPGA devices | - f4pga |

| FPGA tool perf | Framework for automatic FPGA toolchains benchmarking | - fpga-tool-perf - actions |

| OmniXtend | Cache coherence framework for RISC-V based on TileLink | - omnixtend - OmnixtendEndpoint - OmniXtend_RemoteAgent_RISC-V |

| RISCV-DV | Open source verification tool for RISC-V processors | - riscv-dv |

| Intel Compiler for SystemC | Open source SystemC to SystemVerilog translation tool and SingleSource library | - systemc-compiler |

| Chisel | Support the Chisel Hardware Construction Language and related projects | - chisel |

| Working Group | Repo | Description |

|---|---|---|

| Cores TG | Core-v-cores roadmap | |

| CTG meetings and minutes | ||

| CVA6 | 6-stage, application-class core | |

| CVA5 | 5-stage, FPGA-optimized application-class core | |

| CVW | 5-stage, application-class core with education focus | |

| CV32E40P | 4-stage, embedded-class core implementing PULP extensions | |

| CV32E40S | 4-stage, embedded-class core with security focus | |

| CV32E40X | 4-stage, embedded-class core supporting X-Interface | |

| CV32E41P | 4-stage, embedded-class core prototyping Zfinx and Zce | |

| CV32E20 | 2-stage, embedded-class microcontroller core and core complex | |

| CV-HPDCACHE | High performance L1 Data Cache | |

| Verification TG | VTG meetings and minutes | |

| CORE-V Verif | Common test bench for OpenHW Cores | |

| FORCE RISC-V | Advanced RISC-V instruction set generator | |

| ARVM | Advanced RISC-V Verification Methodologies | |

| Software TG | SWTG meetings and minutes | |

| CORE-V GNU Tools | GNU Tools Project for embedded-class CORE-V cores | |

| CORE-V LLVM | LLVM Tools Project for embedded-class CORE-V cores | |

| CORE-V FreeRTOS Kernel | FreeRTOS Kernel for embedded-class CORE-V cores | |

| CORE-V FreeRTOS | FreeRTOS for embedded-class CORE-V cores | |

| CORE-V QEMU | QEMU emulator for CORE-V-MCU | |

| CORE-V SDK | SDK and IDE for embedded-class CORE-V cores | |

| Hardware TG | HWTG meetings and minutes | |

| CORE-V-MCU | ASIC and FPGA MCU implementation of CV32E40P | |

| CORE-V-MCU-DEVKIT | Devkit for CORE-V-MCU | |

| CORE-V-POLARA-APU | Multicore CVA6/CVVEC ASIC with OpenPiton | |

| Technical Working Group | OpenHW project dashboard | |

| Project Description Folders | ||

| OpenHW Project process and templates |