-

Notifications

You must be signed in to change notification settings - Fork 22

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Add cRIO FPGA and Hybrid Mode tests #207

Conversation

This comment was marked as outdated.

This comment was marked as outdated.

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

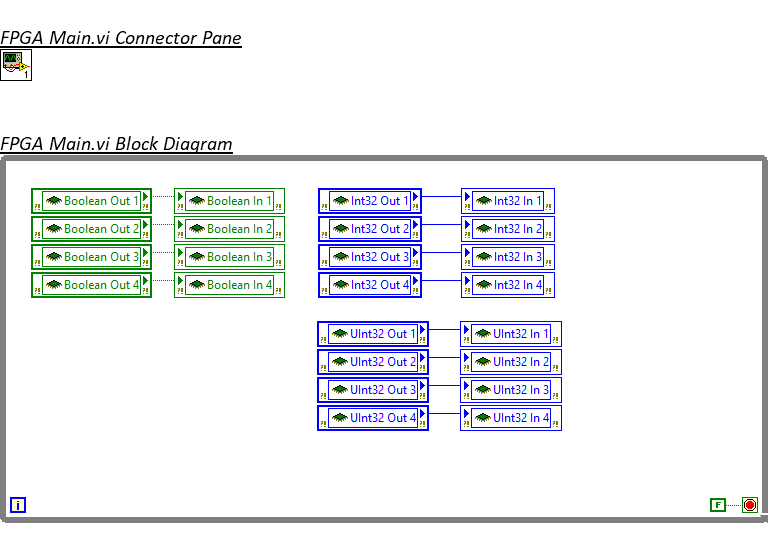

- Separate source for all

FPGA MainVIs. - Update the build specs to output the correct bitfile names to the correct output location for all asset projects.

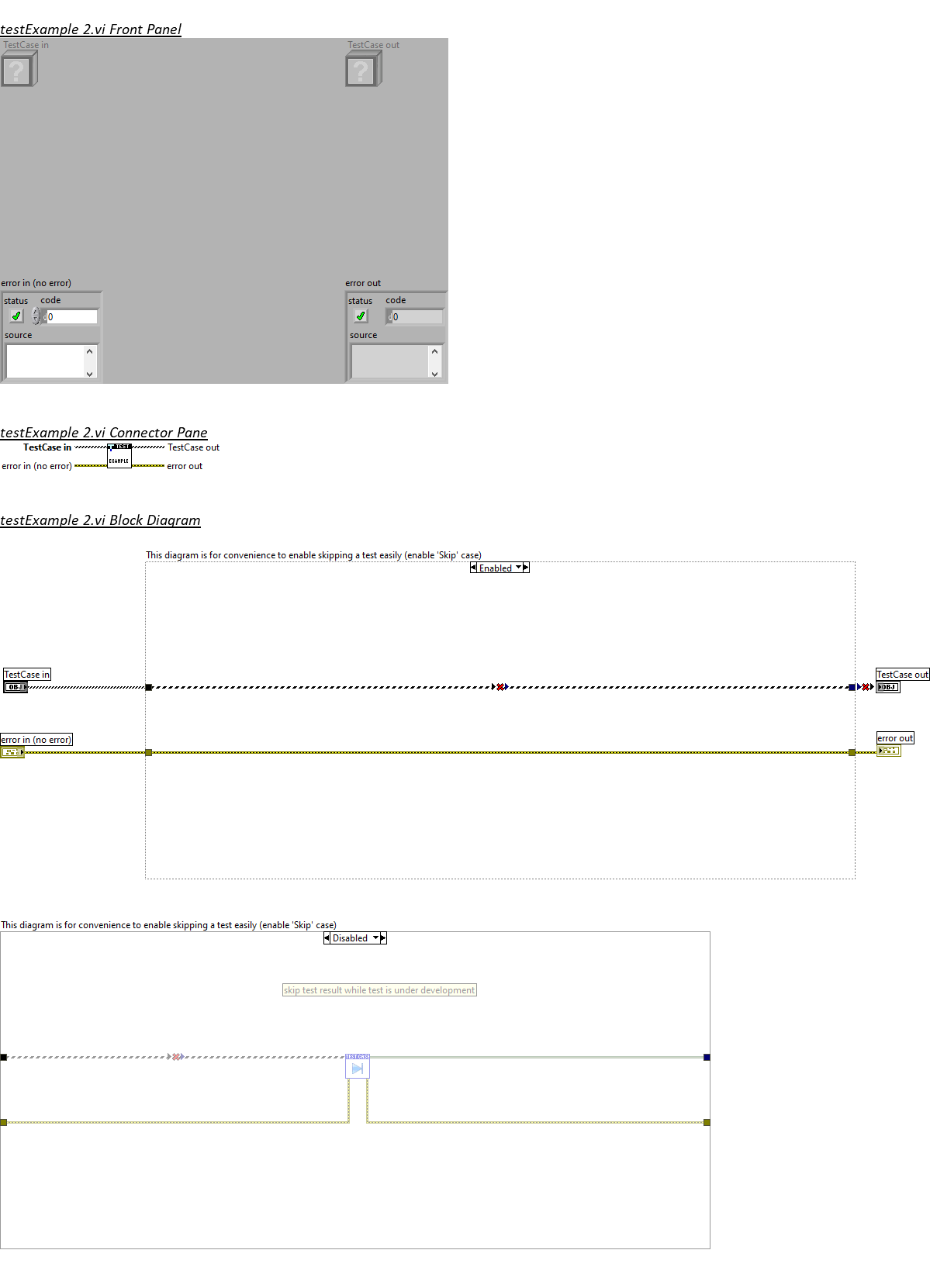

Test VIs look fine. I'm always torn on whether to use random data in tests, but in this instance, I think it's good.

This comment was marked as outdated.

This comment was marked as outdated.

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Approved pending investigation into crashes.

This comment was marked as outdated.

This comment was marked as outdated.

This comment was marked as outdated.

This comment was marked as outdated.

This comment was marked as outdated.

This comment was marked as outdated.

|

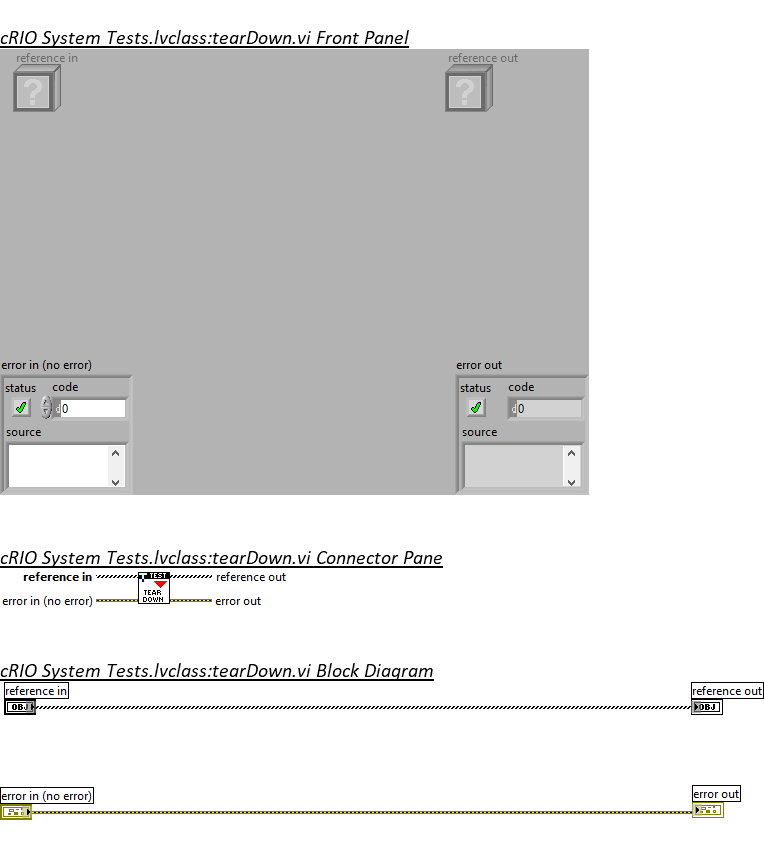

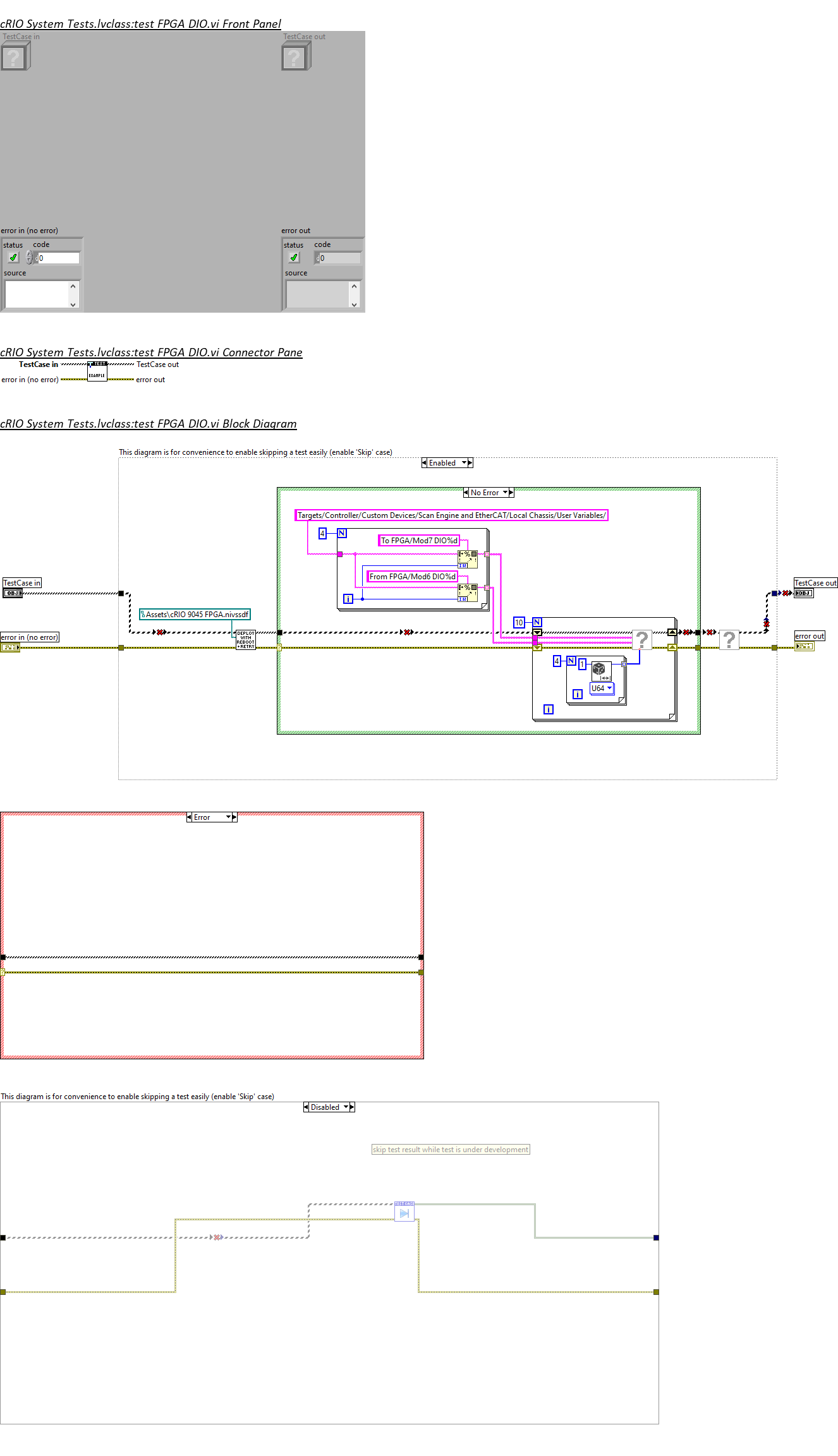

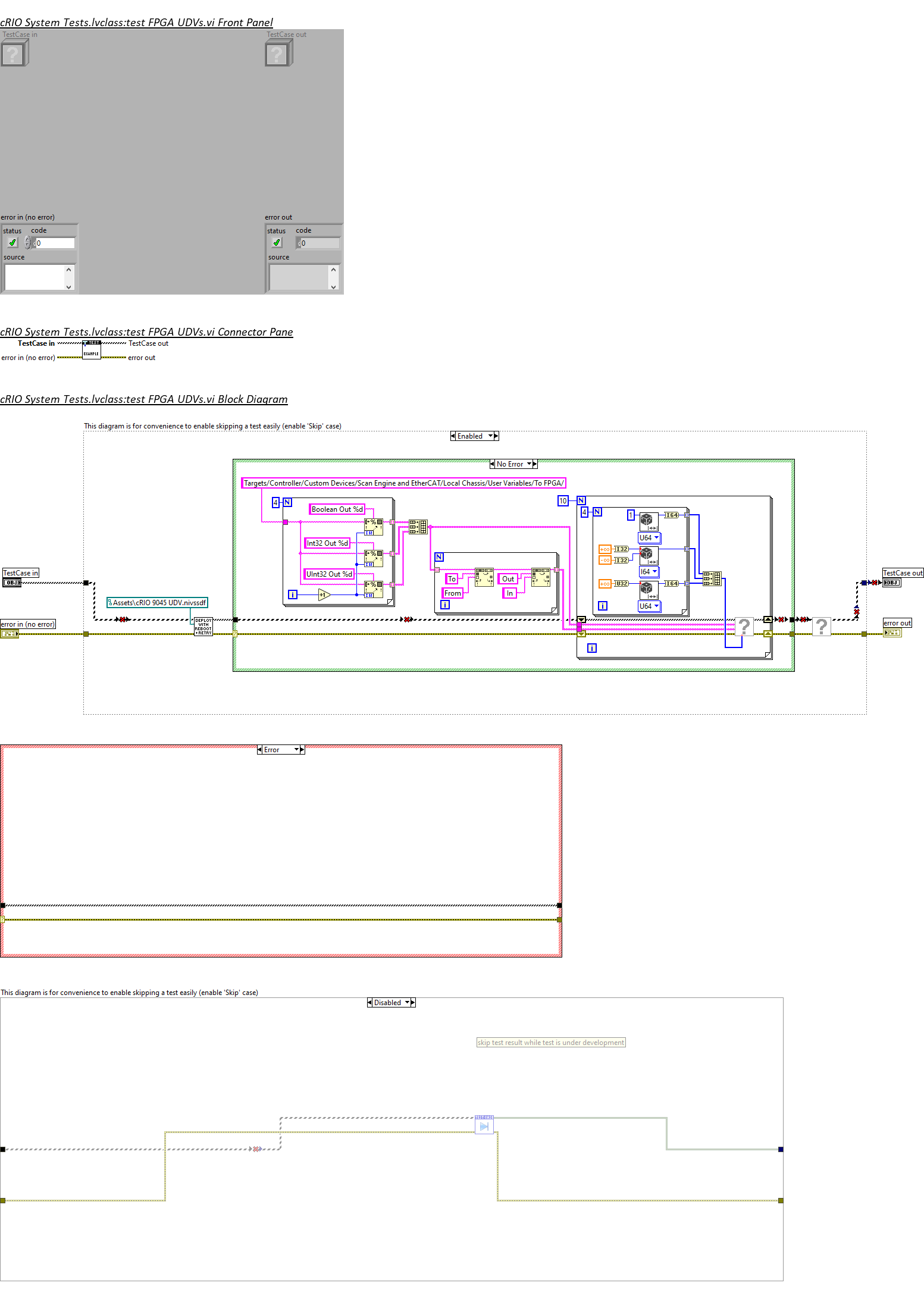

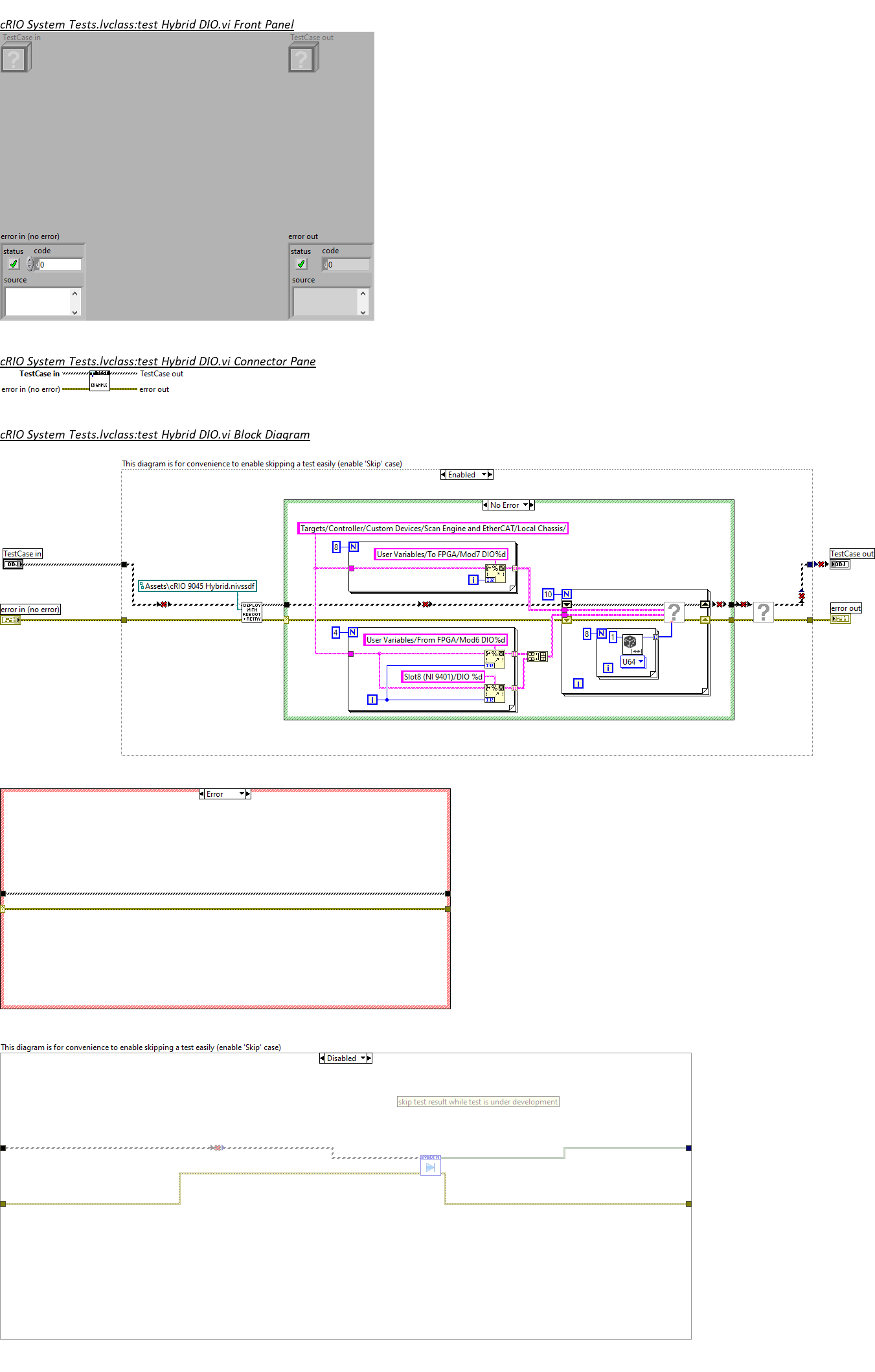

Bleep bloop! LabVIEW Diff Robot here with some diffs served up hot for your pull request. Notice something funny? Help fix me on my GitHub repo. |

What does this Pull Request accomplish?

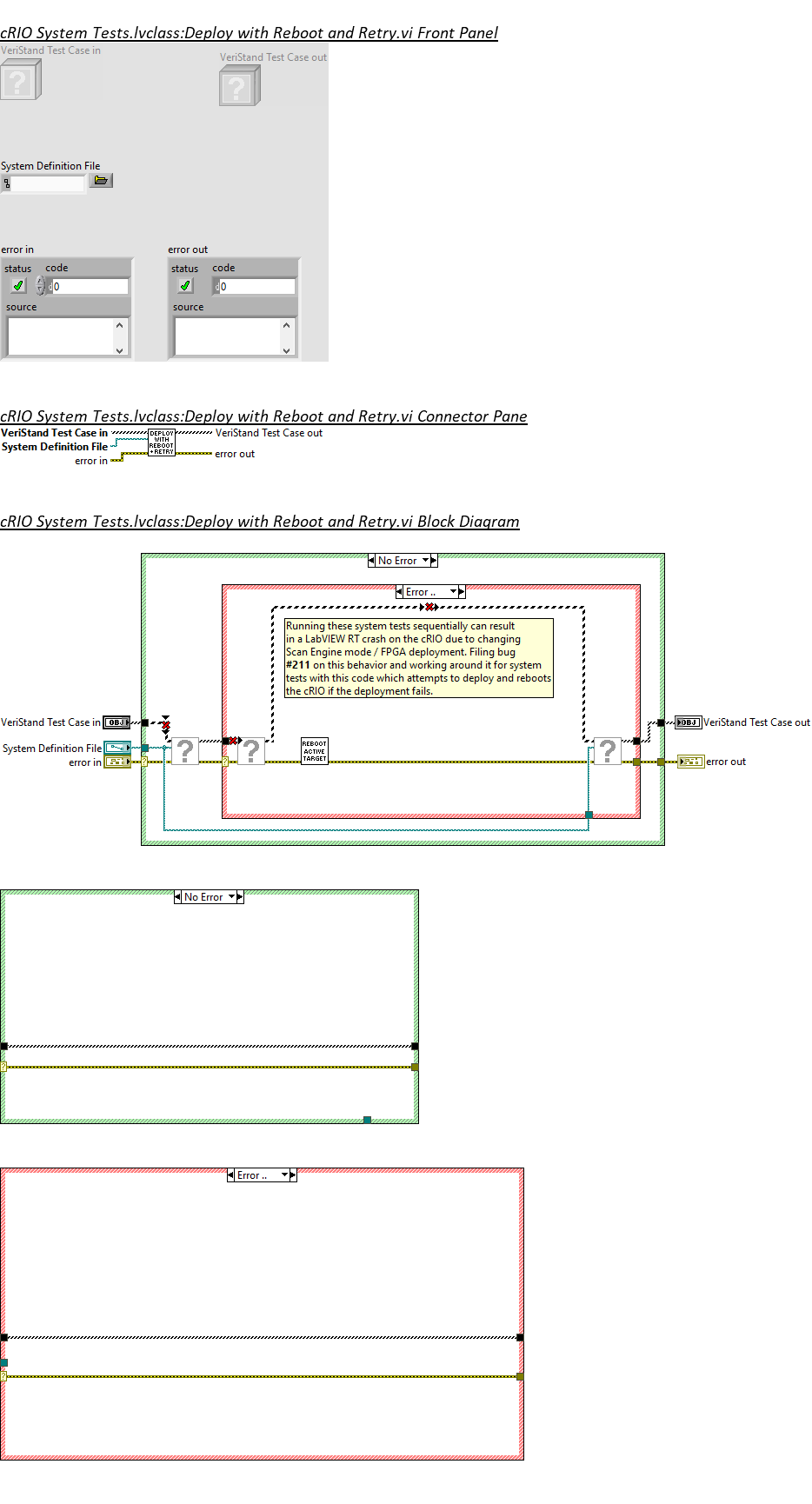

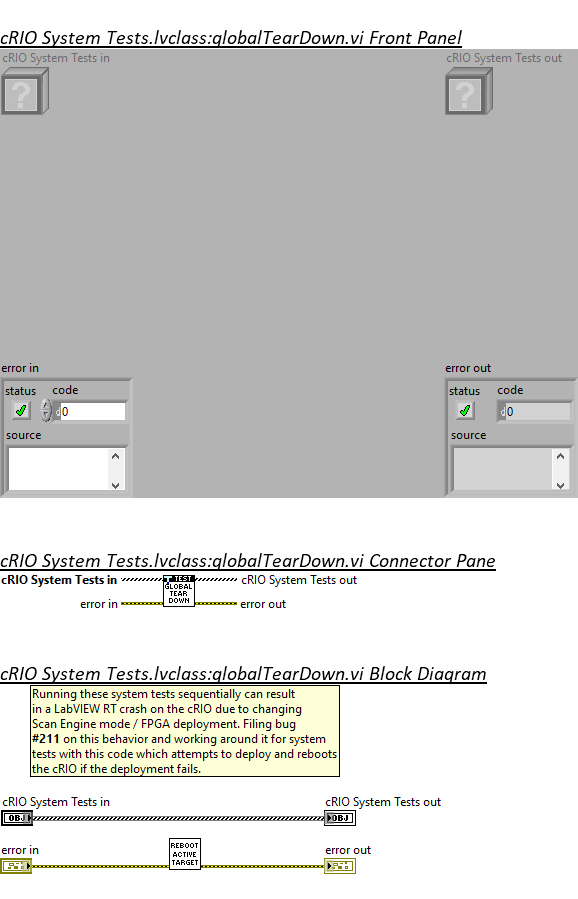

Workaround for Issue #211

When the new tests are run individually, they pass. When run sequentially, LabVIEW RT / VeriStand engine is prone to crashing, which results in various errors.

I filed issue #211 from this failure, and this PR works around the issue for now:

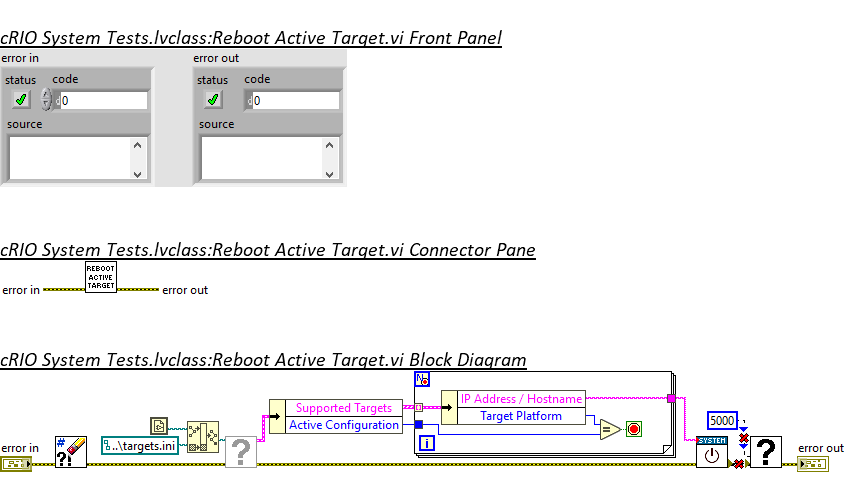

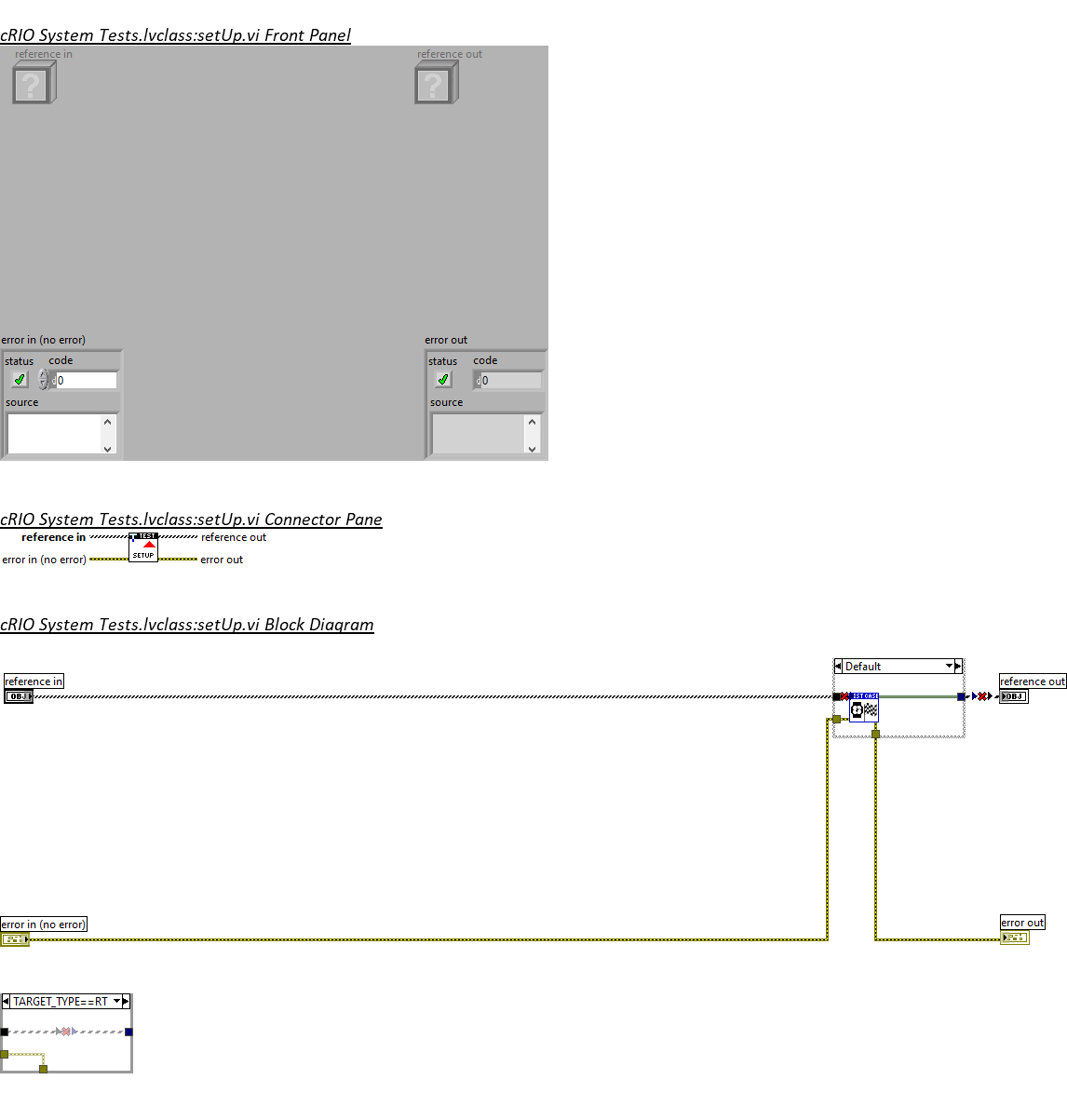

Deploy with Reboot and Retry.viandReboot Active Target.viglobalSetUp.viWhy should this Pull Request be merged?

More fully test the ability for the custom device (and VeriStand) to support Combo cRIO targets.

What testing has been done?

Ran the tests against the ATS cRIO.